# Slide 1:

In fixed partitions, the system needs only to maintain a fixed table with start and end addresses of partitions. When partitions vary dynamically, a more complex data structure is needed.

# Slide 2:

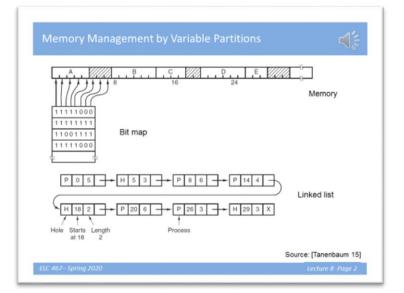

Here, the system will maintain a map of memory indicating free and assigned areas. If this map shows the status of each address (byte), its size will be too large, taking itself a large portion of memory. Thus, map deals with larger units (blocks of addresses) to make its size more compact. Process is assigned an integer number of these allocation units, as map does not handle fractions of units. Unit should not be too large, as process may waste memory if assigned a large unit not used completely.

# Slide 4:

In this alternative method system uses a linked list with a node for every memory partition, whether free or assigned. As partitions are created, split, and merged, the linked list is updated to reflect these changes.

# Slide 4:

# Slide 3:

Note here how memory is divided into units, with a bit in map corresponding to each unit. Process A is assigned the first five units. This is reflected in map by five 1 bits. There is next three free units shown in map by three zero bits,... etc. A search of a free partition with a given size will be a search for a specific number of adjacent zero bits in map.

## Slide 5:

Linked list has a node for each area assigned to process (P) or free or hole (H). Node indicates length of partition and where it starts. Note that units are not necessary for the linked list method and used here for illustration only. If for example process B terminates, the area it occupies will be merged with the preceding hole, forming a single hole of length 9.

# <u>Slide 6:</u>

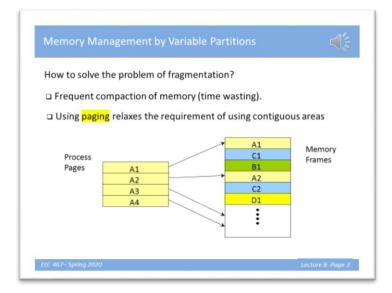

Fragmentation means that after operating for a while, free memory available becomes divided into small areas. Each of these areas cannot be used alone to run any process, since we still assume that process needs to run in an undivided area.

#### Slide 7:

This means to stop system operation occasionally and rewrite the memory contents into adjacent areas, thus grouping the free areas together. This usually results in long delays that slows down the system operation.

#### Slide 8:

With paging, memory contents are divided into fixed size pages. Physical RAM is also considered as a number of frames each having the size of a page. The page contents can be loaded into any free frame. For example, in the shown diagram first page of process A is loaded in first frame. However, second page is loaded in fourth frame since second and third frames are loaded with pages of processes B and C. Thus, memory area used by process no longer need to be undivided. We will consider paging in more detail later.

### Slide 9:

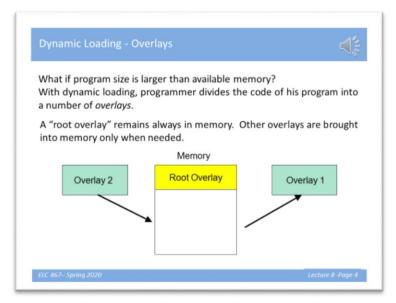

We also assume so far that process cannot run unless all the instructions and data it needs are loaded into memory. Of course, this limits the number of processes that can run concurrently. In fact, typically the process needs only a subset of this information at any time during its execution. It only accesses some instructions and some variables for some time, then moves to other instruction and data,...etc. This is known as the "principle of locality of access".

### Slide 10:

One method that made use of this principle is the method of overlays used in some old systems (e.g. DOS). Compilers under these systems allow user to compile his program into a number of files used one at a time, instead of compiling it into a single large executable file.

#### <u>Slide 11:</u>

For example, a word processor program may have an overlay file for editing functions, and another overlay file for spelling check. Since these will not be used together, this allows process to run from a smaller memory area. However, this method depends on the programmer for dividing the code and does not do this automatically. Also, it applies for instructions and not data. These disadvantages are solved in the method of virtual memory considered next.

# Slide 12:

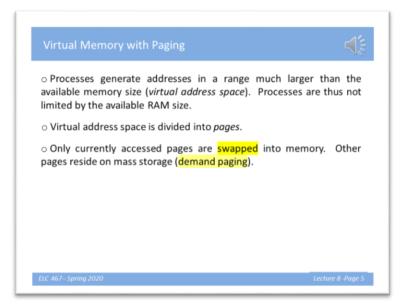

We consider the method of virtual memory combined with paging since this is how it is used in current processors. The method of virtual memory allows processes to run without restrictions resulting from the available physical RAM size.

# <u>Slide 13:</u>

Each process can access addresses in a very large address space (typically of terabytes) irrespective of actual RAM size, and number of processes concurrently sharing the RAM. This is known as the virtual address space.

# Slide 14:

Demand paging means that page will be brought into a RAM frame (or swapped in it) only when process starts to access its contents. If page is not accessed, it remains on disk (in a special swapping file). Thus, in a sense, a part of disk acts as an extension to RAM.

### <u>Slide 15:</u>

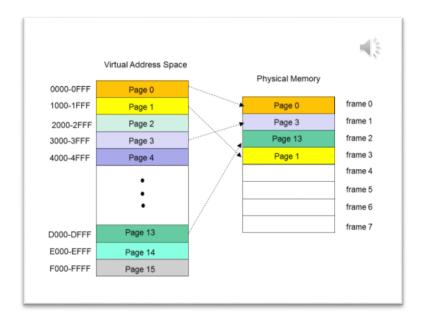

We consider this example with very small sizes for illustration only. Here, each process behaves as if it has access to 64K of memory, although actual RAM size is 32K. Page size is 4K, thus virtual space has 16 pages and physical memory has 8 frames.

### <u>Slide 16:</u>

Process starts to access addresses in page 0 (e.g. to fetch instructions). Thus, the contents of this page are swapped into a free frame, for example frame 0. Addresses used by the process will be from 0000 to 0FFF. These are the same physical addresses of frame 0, so no translation from virtual to physical addresses will be necessary.

### <u>Slide 17:</u>

Now process reads data from the address range of page 3. This is now swapped into frame 1. Note that address translation from the virtual range of page 3 (3000-3FFF) to the physical range of frame 1 (1000-1FFF) is now necessary with each access.

### <u>Slide 18:</u>

Process now accesses the stack while the stack pointer is pointing to an address in page 13. Thus, page 13 is brought into frame 2. Again, page translation will be necessary.

#### <u>Slide 19:</u>

Process now fetched all instruction in page 0 and starts fetching instructions from page 1. This is swapped into frame 3. The other eleven virtual pages will not be brought into RAM frames until demanded by the process.

#### Slide 20:

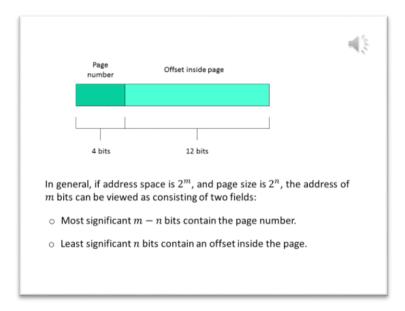

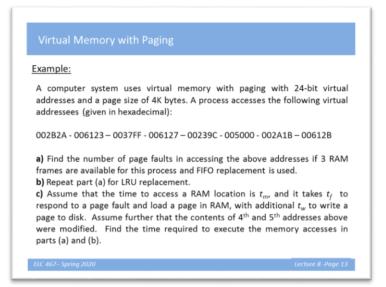

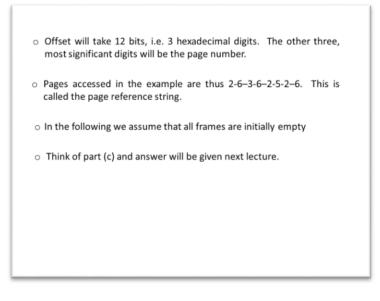

By inspection of addresses in the previous simplified example, it is seen that most significant hexadecimal digit of address (4 bits) is actually the page number. Other digits give a range of offsets that is repeated in each page. This can be generalized as shown here.

| Virtual Addresses are tr<br>table.<br>Page # offset<br>Virtual<br>Address |  | ical addresses using a page |

|---------------------------------------------------------------------------|--|-----------------------------|

|---------------------------------------------------------------------------|--|-----------------------------|

### <u>Slide 21:</u>

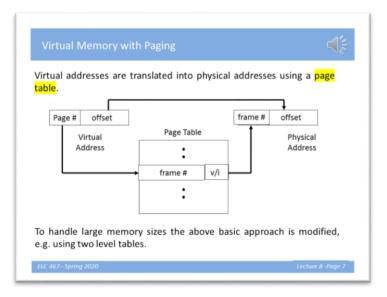

Translation will be in fact simple. To translate virtual address into physical address, we need to know the number of frame in which page is loaded, then simply replace the page number with the frame number, keeping offset the same. More on this slide later.

| Virtual Memory with Paging                                                                                                                                                          | 4:                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <ul> <li>Processes generate addresses in a range much larg<br/>available memory size (virtual address space). Processes<br/>limited by the available RAM size.</li> </ul>           |                   |

| <ul> <li>Virtual address space is divided into pages.</li> </ul>                                                                                                                    |                   |

| <ul> <li>Only currently accessed pages are swapped into mer<br/>pages reside on mass storage (demand paging).</li> </ul>                                                            | nory. Other       |

| <ul> <li>Swapping of pages in and out of memory is done by t<br/>system and is transparent to the user.</li> </ul>                                                                  | he operating      |

| <ul> <li>For efficient operation, virtual memory must be suppliardware which translates virtual addresses to physic using parts of process page table cached in the TLB.</li> </ul> |                   |

| ELC 467– Spring 2020                                                                                                                                                                | Lecture 8 -Page 5 |

#### <u>Slide 22:</u>

The user needs not be concerned by the process of swapping of demanded pages. This will be the responsibility of the operating system. In fact, user will not be aware of this process unless heavy swapping causes the system to be somewhat slower.

#### Slide 23:

If continuous translation of addresses is done by software, system will be too slow to be practical. Thus, processor hardware must support this translation process. A page table holds where each virtual page is loaded in physical RAM. This is stored (at least partially) inside processor in the so called TLB, which stands for Translation Lookaside Buffer.

### Slide 24:

A straightforward structure of page table will have an entry for each page. A valid/invalid bit is set if page is present in memory and is 0 otherwise. In the first case, the number of frame in which page is loaded is written in table.

#### <u>Slide 25:</u>

With actual huge address spaces with large number of pages, table constructed in this way will be too large to be stored within processor. Thus this simple form need to be modified.

#### Slide 26:

For example, consider the case of 32-bit virtual addresses and 4K pages. The 4G address space will have million virtual pages, and page table should have million entries. Instead, we may consider that we have 1024 tables, with 1024 entries each. This corresponds to the shown fields of address. Benefiting again from the locality of access, we hold one table at a time within the processor.

| Virtual Memory with Paging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         | <b>₹</b>          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|

| 0 A<br>1 B<br>2 C<br>3 D<br>4 E<br>6 F<br>6 G<br>7 H<br>bgical<br>memory usid-invalid<br>frame bit<br>0 4 V<br>1 1<br>2 6 V<br>3 i<br>1 0<br>2 6 V<br>1 1<br>2 8 V<br>1 1<br>1 1<br>1 1<br>1 1<br>1 1<br>1 1<br>1 1<br>1 | 0<br>1<br>2<br>3<br>4<br>4<br>5<br>6<br>C<br>7<br>8<br>9<br>7<br>8<br>9<br>7<br>12<br>13<br>14<br>15<br>physical memory |                   |

| ELC 467-Spring 2020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                         | Lecture 8 -Page 8 |

## <u>Slide 27:</u>

This is another illustration of the previous discussion. Virtual memory can also be called logical memory, as opposed to physical memory. Here, process has 8 pages of which three pages A,C, and F are swapped from disk shown on the right into physical memory frames. Note that there are two copies of the contents of each of the three demanded pages: one on disk and one in RAM.

|                                                                                            | ory address in a page which is not curs, typically causing an interrupt. |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| In response to this interrupt, t following sequence:                                       | he operating system executes the                                         |

| - It looks for an empty RAM fran<br>and swaps it to disk to empty a f                      | ne. If no one exists, it selects a page rame.                            |

| <ul> <li>It schedules a disk access to re<br/>This page is written into the emp</li> </ul> | ead the required page from the disk.<br>hty frame.                       |

| - It modifies the page table(s) acc                                                        | ordingly.                                                                |

| - The execution of the proce<br>instruction in which the page fau                          | ss is restarted starting from the toccurred.                             |

### <u>Slide 28:</u>

Now we explain how page swapping is handled. If an address in a page not present in physical memory is accessed, a page fault interrupt occurs.

#### Slide 29:

We will consider later which page should be swapped out of RAM if no frame is available.

### <u>Slide 30:</u>

The term "schedules an access" is used since probably other disk access operation is currently taking place. We will understand this more when we study file management.

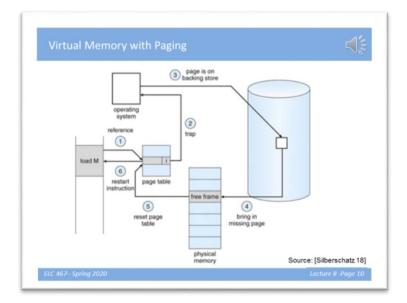

## Slide 32:

You should be able now to understand the steps in this diagram. The term "trap" in step 2 is usually used to refer to interrupts resulting from errors, a page fault in this case.

| Virtual Memory with Paging                                                                                                                   |                         |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Page Replacement Algorithms                                                                                                                  |                         |

| If all frames are loaded and a new page is accessed, w swap out of physical memory?                                                          | hich page to            |

| Ideally, the page replacement algorithm must <i>minimize th</i> page faults. This can't be achieved since we cannot demanded pages a priori. |                         |

| First-in-first-out (FIFO) replacement                                                                                                        |                         |

| Swap out the page that was first loaded into memory.                                                                                         |                         |

| However, a page that was loaded earlier than others m use.                                                                                   | ay still be in          |

| ELC 467– Spring 2020                                                                                                                         | _<br>Lecture 8 -Page 11 |

#### Slide 34:

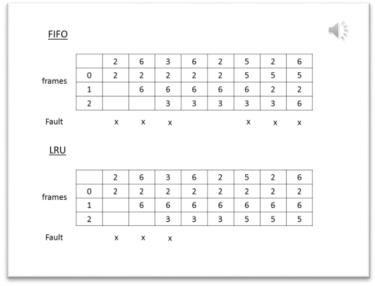

Ideally, the page swapped out should be a page that will not be accessed or demanded again. Unfortunately, system will not be able to know exactly which addresses the process will access in the future. Note that if page contents were modified while in RAM, copy of page on disk need to be updated when swapped out causing an additional disk write operation.

#### Slide 35:

FIFO is based on the assumption that the page that was first brought into memory was there for a long time, and is expected to be no longer needed. On the other hand, a page just swapped in is most probably still in use.

#### Slide 36:

This assumption is not necessarily true. For example, a page containing the instructions of a loop with many iterations will remain in use for long time, although loaded earlier than other pages.

| Swap | out the p | bage that has no | t been accessed fo | r the longe | est period. |

|------|-----------|------------------|--------------------|-------------|-------------|

| Exam | ple:      |                  |                    |             |             |

|      | Page      | Loading time     | Last access time   | modified    | 1           |

|      | 0         | 126              | 279                | 0           | 1           |

|      | 1         | 230              | 260                | 0           | 1           |

|      | 2         | 120              | 272                | 1           | 1           |

|      | 3         | 160              | 280                | 1           | 1           |

#### Slide 37:

This method takes into account whether page is still in use or not. It swaps out the page which was not used for a longer time.

#### Slide 38:

Note however that LRU can be implemented without storing the time of each access, which is not practical. We will consider some alternative methods in the problem set.

# <u>Slide 41:</u>

In LRU, when page 5 was accessed the page that was not accessed for the longest time was page 3. Thus, this is the one swapped out, although loaded after pages 2 and 6, which were accessed after it.